MakeTestBench

version 1.702

MakeTestBench is een programma dat speciaal voor het lab Digitaal Ontwerpen is ontwikkeld. MakeTestBench genereert een testbench voor een VHDL-beschrijving. Het is geschikt voor combinatorische and sequentiële beschrijvingen. Deze handleiding hoort bij MakeTestBench versie 1.702 van MakeTestBench.

Belangrijk om te weten is dat MakeTestBench geen codechecker is. De applicatie zoekt in een VHDL-bestand de naam van de entity, de architecture, de in- en uitgangssignalen en de generics op en maakt hiermee een opzet voor een testbench. De code van het VHDL-bestand moet correct zijn. Code, die niet aan de de VHDL-syntax voldoet, kan een onzinnige resultaat geven.

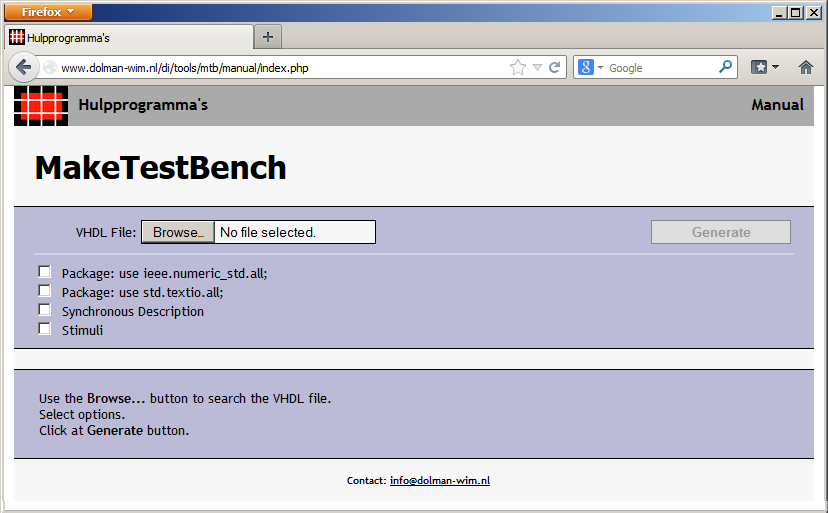

Start MakeTestBench

Dit is het introductievenster:

[Dit is het uiterlijk met Firefox. Met een andere browser kan de interface er anders uitzien.]

Met het bovenstaande blauwe vlak wordt het VHDL-bestand en worden de opties ingesteld. In het tweede blauwe val staan hints, foutmeldingen of waarschuwingen.

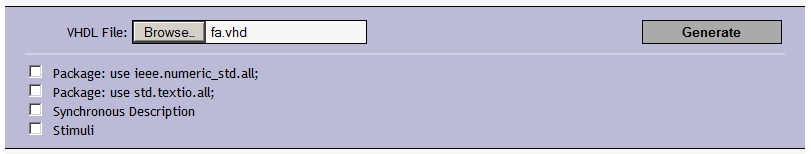

Selectie van het VHDL-bestand zonder opties

In het veld VHDL File moet de bestandsnaam worden ingevuld. Met de knop naast VHDL File zoek je het VHDL-bestand op waarvoor je een testbench wilt maken. Dit bestand moet minimaal de entity en een architecture van de beschrijving bevatten. De architecture mag leeg zijn.

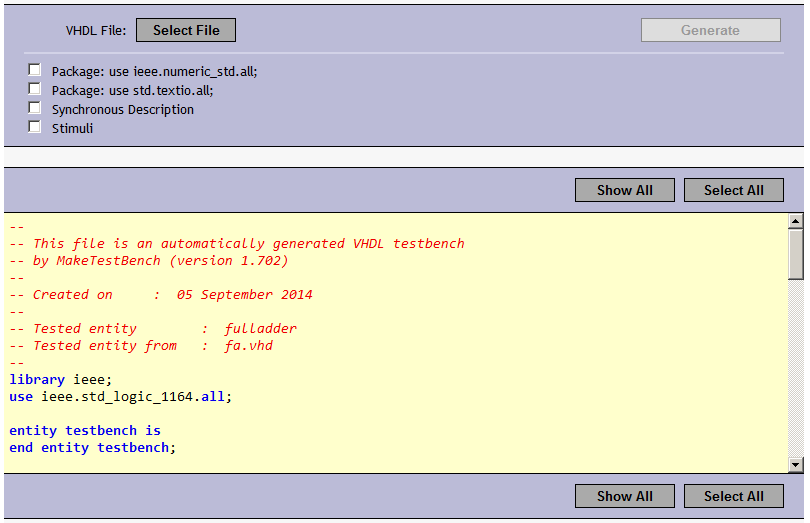

Nadat je een bestand geselecteerd hebt, wordt de Generate-knop actief. Met een klik op Generate krijg je de gegenereerde testbench in een apart veld te zien.

Met de knop Select All kun je de complete code selecteren.

Met ctrl-C kopieer je de geselecteerde code naar het clipboard en

met ctrl-V kun je deze code in een teksteditor plakken en daarna opslaan.

Geef dit bestand dezelfde naam als het VHDL-bestand met een prefix tb_.

Bij het VHDL-bestand fa.vhd hoort dan de testbench tb_fa.vhd.

Met de knop Show All maak je de hele code zichtbaar.

De Generate is weer inactief. Als je een andere testbench wilt maken, moet op Select File klikken en opnieuw een bestand selecteren.

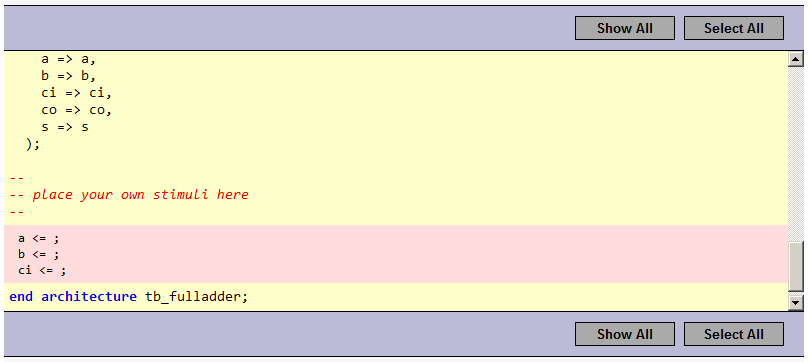

MakeTestBench maakt alleen een testomgeving. De testvectoren of stimuli moet de gebruiker zelf toevoegen via de stimuli optie of naderhand aan de testbench toevoegen. MakeTestBench weet immers niet hoe je de code wilt gaan testen.

In dit voorbeeld bevat bestand fa.vhd de beschrijving van een full-adder. Voor een correcte simulatie moeten alle ingangssignalen a, b en ci gedefinieerd zijn. Alle ingangssignalen uit de originele VHDL-beschrijving, die niet in de stimuli staan en die niet als klok of als reset worden gebruikt, worden als onvolledige signaaltoewijzingen aan de testbench toegevoegd. De roze achtergrond geeft aan dat de VHDL-code hier nog niet compleet is.

De opties van MakeTestBench

Toevoegen packages

Als je de checkboxen Package: use ieee.numeric_std.all en Package: use std.textio.all aanvinkt, worden deze regels bij de bibliotheek en package definities aan de code toegevoegd:use ieee.numeric_std.all; use std.textio.all;

Synchrone beschrijving

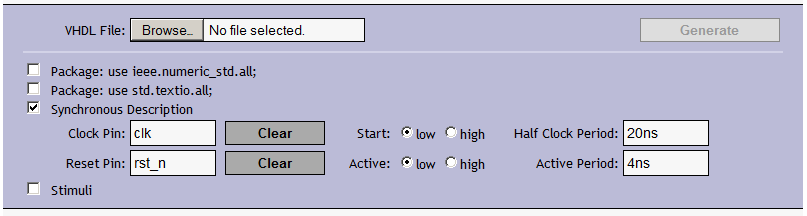

Als je Synchronous Description aanvinkt, dan wordt de interface uitgebreid met de instellingen voor de klok en de reset. Deze instellingen zijn nuttig bij een VHDL-beschrijving van een sequentiële schakeling.

Standaard maakt MakeTestBench een kloksignaal clk dat laag begint

en een periodetijd van 40 ns heeft en een actief laag resetsignaal rst_n.

Als de klok- en resetnaam in de portlist van de entity staan,

worden aan de testbench deze regels toegevoegd:

constant HALF_CLOCK_PERIOD : time := 20 ns; constant RESET_PERIOD : time := 4 ns;

clk <= not clk after HALF_CLOCK_PERIOD; rst_n <= '1', '0' after RESET_PERIOD;en bij de declaratie van de klok wordt de beginwaarde toegevoegd:

signal clk : std_logic := '0';

Als de klok- of resetnaam niet voorkomt in de portlist van de entity, verschijnt

er bij de generatie van de testbench een waarschuwing en wordt de betreffende instelling genegeerd.

De halve periodetijd en de actieve periode mogen met en zonder spaties worden opgeschreven.

Dus 20ns en

20 ns zijn beide correct.

MakeTestBench maakt er altijd 20 ns van.

Toevoegen stimuli

Als je Stimuli aanvinkt, kun je een bestand met stimuli toevoegen of de stimuli in twee tekstvelden invullen. Je kunt natuurlijk ook later de stimuli aan de testbench toevoegen.

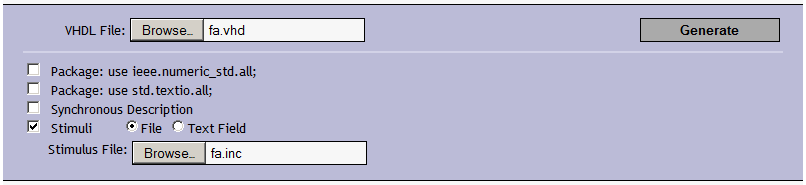

Toevoegen van een bestand met stimuli

Een bestand met stimuli kun je deze insluiten door

Stimuli aan te vinken, de optie File

te selecteren en bij Stimuli File het bestand op te zoeken.

Dit bestand moet de extensie .inc hebben.

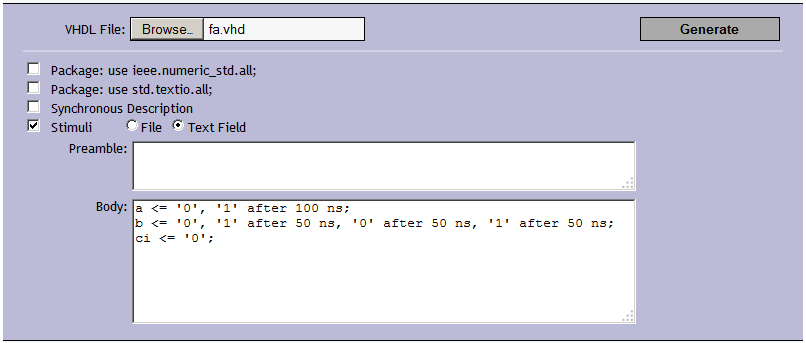

Tekstvelden met stimuli

Je kunt de stimuli ook direct invullen met MakeTestBench. Selecteer daarvoor bij Stimuli en daarna het item Text Field. Eventuele declaraties zet je in het tekstveld Preamble en de signaaltoewijzingen zet je in het tekstveld Body.

De declaraties uit het tekstveld Preamble wordt bij de generatie van de testbench in het declaratiegedeelte van de architecture geplaatst. Alle code uit het tekstveld Body wordt bij de generatie van de testbench in de body van de architecture geplaatst.

De syntax van een bestand met stimuli

Het bestand met stimuli moet de extensie .inc hebben.

In principe wordt alle code de .inc

in de body van de testbench geplaatst.

Een regel, die begint met het woord begin is

een separator, die de stimulusfile in twee delen splitst.

Alles voor deze separator komt in het declaratiegedeelte of de preamble

van de architecture van de testbench en alles dat na deze separator komt in de body

terecht.

Bevat de stimulusfile geen separator wordt alles in de body van de

architecture gezet.

Eindigt het bestand met de separator dan wordt alles in het declaratiedeel

van de architecture of aan het begin van het bestand geplaatst.

library somelibrary; use somelibrary.somepackage.all; constant DELAY : time := 4 ns; signal in1 : std_logic; signal in2 : std_logic;

begin

process begin in1 <= '0'; in0 <= '0'; wait for DELAY; in0 <= '1'; wait for DELAY; in1 <= '1'; wait for DELAY; in0 <= '0'; wait; end process; |

Dit deel wordt aan begin van de testbench bij de andere bibliotheken geplaatst.

Dit deel komt in het declaratiedeel van de architecture van de testbench te staan.

Deze begin is de separator.

Dit deel komt in het declaratiedeel van de architecture van de testbench te staan.

De begin van het proces is geen separator, omdat er spaties voor staan. |

Voor de separator staan dus geen spaties of tabs staan. Daardoor is het mogelijk om processen, procedures en functies in de beschrijving te gebruiken. Voor de begin van een proces, procedure of functies moet dan wel een of meer spaties of tabs staan.

Regels voor de separator, die met use en library beginnen, komen niet in het declaratiedeel van de architecture te staan, maar komen voor de entity bij de andere bibliotheek- en package-definities te staan.

Waarschuwingen en foutmeldingen

MakeTestBench verwacht correct geschreven VHDL als invoer. Als er onduidelijkheden zijn over de invoer, geeft MakeTestBench een foutmelding of een waarschuwing. Bij een foutmelding wordt er geen code gegenereerd. Bij een waarschuwing wordt er wel een testbench gemaakt.

MakeTestBench doet geen codechecking. MakeTestBench leest in principe alleen de generic- en de portlist van de entity. Als de ingevoerde VHDL-code niet correct is, kan de testbenchgeneratie vastlopen. In dat geval wordt na enige tijd de generatie automatisch gestopt zonder uitvoer te genereren en zonder foutmelding. Dit laatste kan ook gebeuren als de generic- of de portlist zeer complexe datatypen bevat.